G1oba1c2h5ohვერილოგის მაგალითები

https://www.edaplayground.com/playgroundsსხვადასხვა ლეველზე შეგიძლია რა პროგრამირება

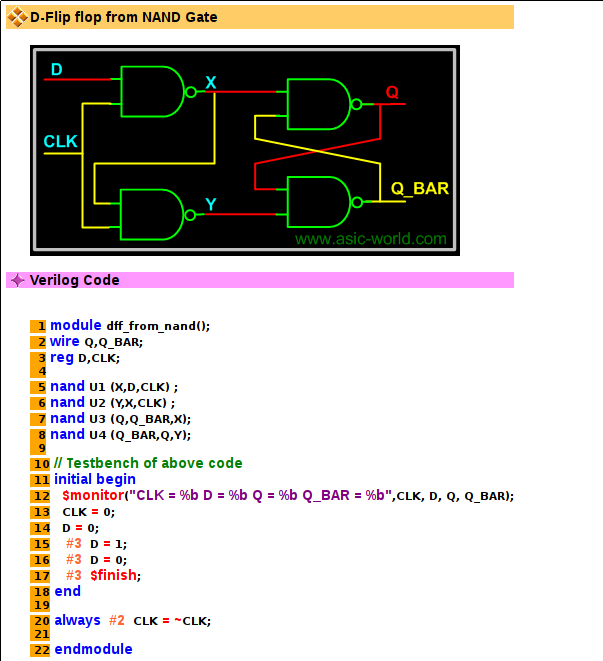

gate level, პირდაპირ გეითების ინფუთებს და აუთფუთებს უთითებ

მაგალითები:

http://www.asic-world.com/verilog/gate2.htmlflip flop ის მაგალითი:

მე5 ხაზი არის მაგალითად ზედა მარცხენა nand გეითის კოდის, აუთფუთი აქვს x da ინფუთები clk და d.

ფაქტობრივად უთითებ რა გეითი ჩააგდოს და რა რასთან მიაერთოს.

11 დან 18 ის ჩათვლით ხაზები არაა საჭირო სქემა რაც ჩანს იმის სინთეზისთვის, ტესტბენჩია, ანუ სიმულატორში ტესტავ კონკრეტულ ინფუთებზე იმ აუთფუთებს თუ გაძლევს რასაც უნდა იძლეოდეს სინთეზირებული სქემა, მაგრამ სიმულაცია და რეალურად სინთეზირებული სქემა არ ემთხვევა ყოველთვის.

შეგიძლია RTL ლეველზე დაწერო კოდი,

RTL ში შეგიძLია გამოიყენო რეგისტრებიც და სხვა რამეებიც რისი ფიზიკურად სინთეზირებაც შეიძლება FPGA ბორდზე.

აქაა მაგალითები

https://www.doulos.com/knowhow/verilog_desi...de/rtl_verilog/behavioral ლეველში უკვე ლუპების და conditional სთეითმენთების და ეგეთების გამოყენებაც შეგიძლია,

რა თქმა უნდა პირდაპირ ამ ყველაფერს ვერ დაასინთეზებ, შენი კოდის RTL ვარიანტს თვითონ მოიფიქრებს კომპილატორი.

This post has been edited by execution on 26 Jun 2018, 11:07